## CS 211: Intro to Computer Architecture 9.2: RISC-V Assembly

## **Minesh Patel** Spring 2025 – Thursday 27 March

## Announcements

- •Assignments

- PA3: due Friday @ 23:59

- Extra Credit: replaces WA6, due in two weeks

# Inside a Processor Lots of Pictures

Inside a Processor Core

Cache and Register Memory

•RISC-V Assembly

- Instructions and Opcodes

- Immediate Values

- •Function Arguments

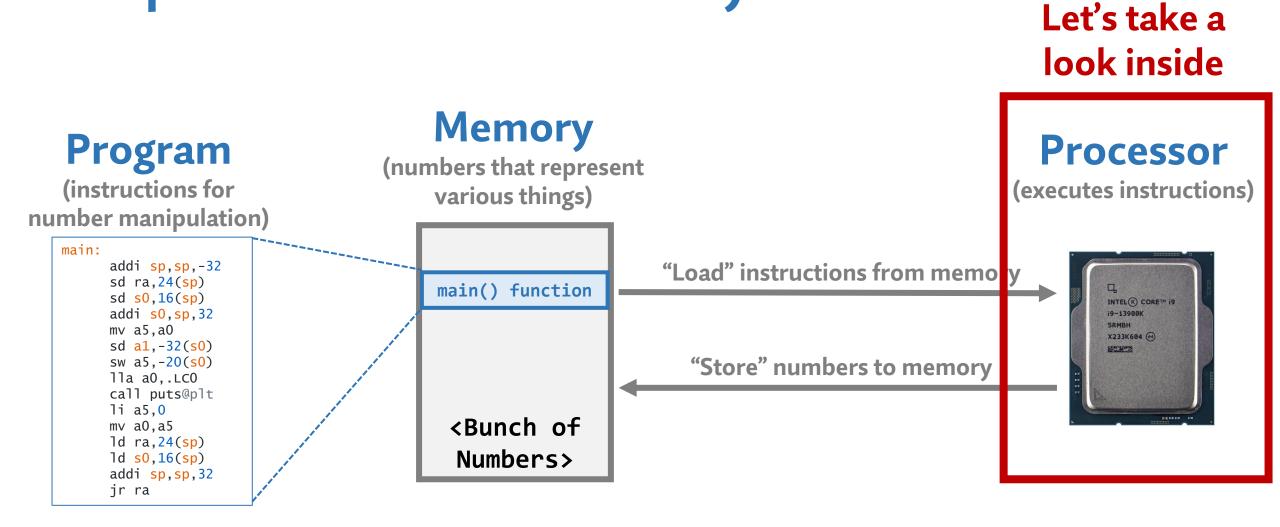

## **Recap: Processor and Memory**

## "From Sand to Silicon"

Intel, "Making of a Chip Illustrations," January 2012.

#### Sand

Silicon is the second most abundant element in the earth's crust. Common sand has a high percentage of silicon. Silicon - the starting material for computer chips - is a semiconductor, meaning that it can be readily turned into an excellent conductor or an insulator of electricity, by the introduction of minor amounts of impurities.

#### Melted Silicon -

scale: wafer level (~300mm / 12 inch) In order to be used for computer chips, silicon must be purified so there is less than one alien atom per billion. It is pulled from a melted state to form a solid which is a single, continuous and unbroken crystal lattice in the shape of a cylinder, known as an ingot.

Monocrystalline Silicon Ingot scale: wafer level (~300mm / 12 inch) The ingot has a diameter of 300mm and weighs about 100 kg.

Copyright © 2012, Intel Corporation. All rights reserved. Intel, Intel logo and Intel Core are trademarks of Intel Corporation in the U.S. and other countries.

## "From Sand to Silicon"

Intel, "Making of a Chip Illustrations," January 2012.

#### Ingot / Wafer

#### Ingot Slicing -

scale: wafer level (~300mm / 12 inch) The ingot is cut into individual silicon discs called wafers. Each wafer has a diameter of 300mm and is about 1 mm thick.

#### Wafer -

scale: wafer level (~300mm / 12 inch) The wafers are polished until they have flawless, mirror-smooth surfaces. Intel buys manufacturingready wafers from its suppliers. Wafer sizes have increased over time, resulting in decreased costs per chip. when Intel began making chips, wafers were only 50mm in diameter. Today they are 300mm, and the industry has a plan to advance to 450mm.

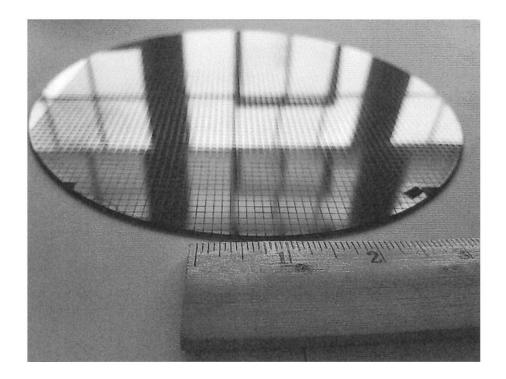

## SiFive RISC-V Processor Wafer

**Figure 1.16** This 200 mm diameter wafer of RISC-V dies was designed by SiFive. It h two types of RISC-V dies using an older, larger processing line. An FE310 die is 2. mm  $\times$  2.72 mm and an SiFive test die that is 2.89 mm  $\times$  2.72 mm. The wafer contai 1846 of the former and 1866 of the latter, totaling 3712 chips.

Hennessy and Patterson, "Computer Architecture" 6/E.

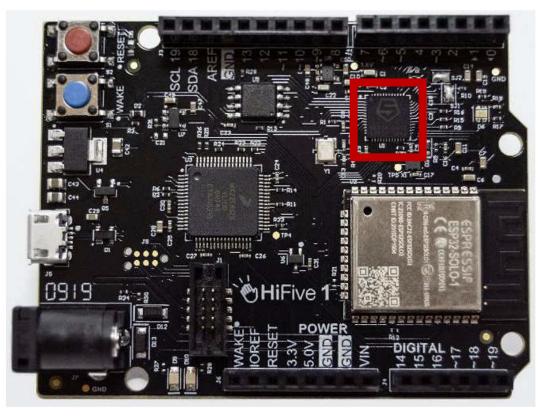

# HiFive 1 Rev B01

SiFive, "HiFive1 Rev B Schematics," 2021.

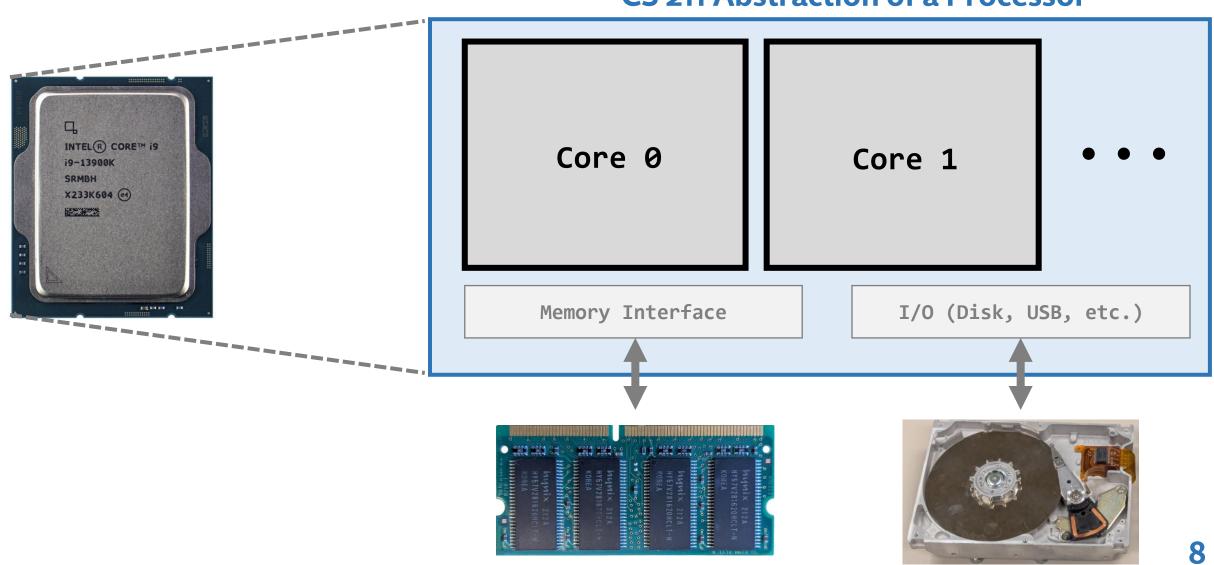

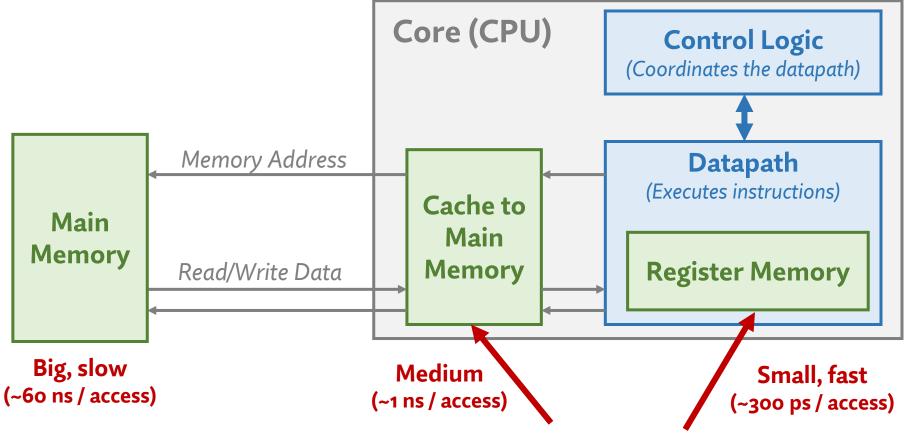

## Mental Model: What's Inside a Processor?

#### CS 211 Abstraction of a Processor

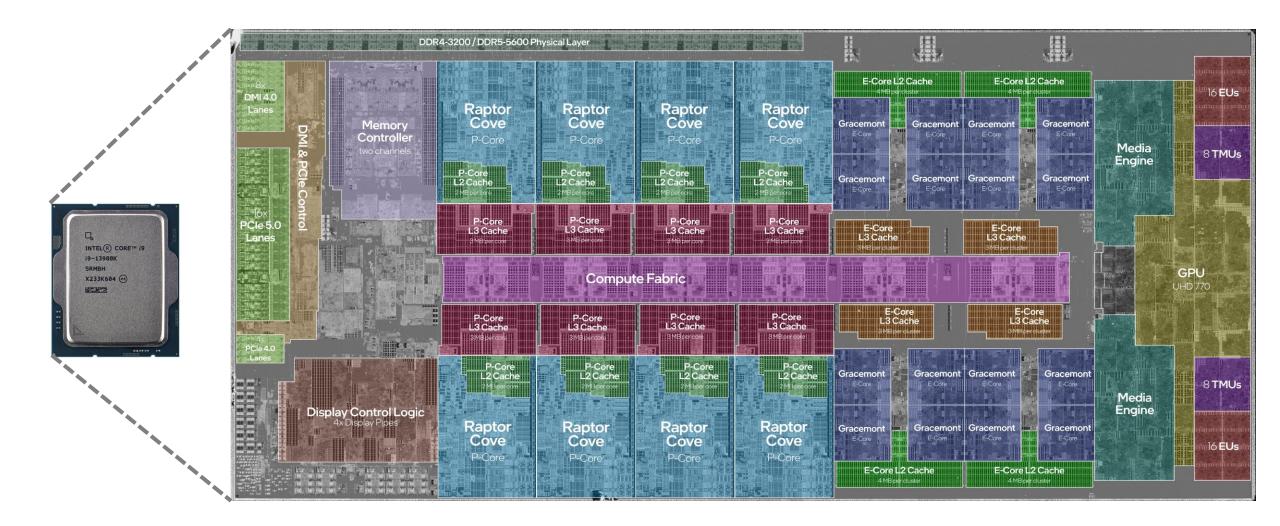

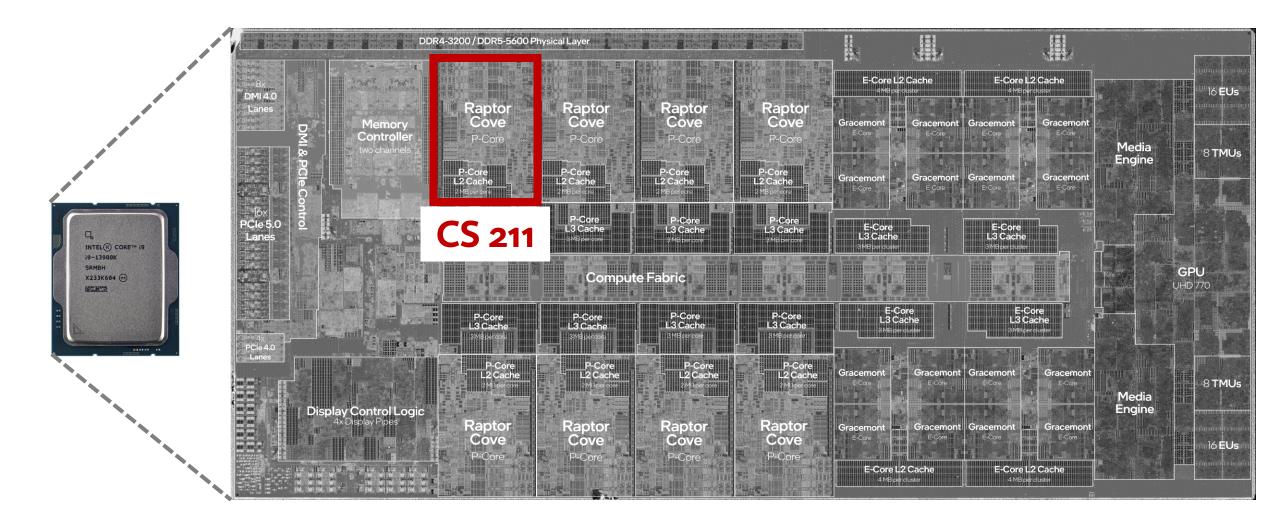

## Inside an Intel i9-13900K

## Inside an Intel ig-13900K

# Inside a Processor Lots of Pictures Inside a Processor Core Cache and Register Memory

•RISC-V Assembly

- Instructions and Opcodes

- Immediate Values

- •Function Arguments

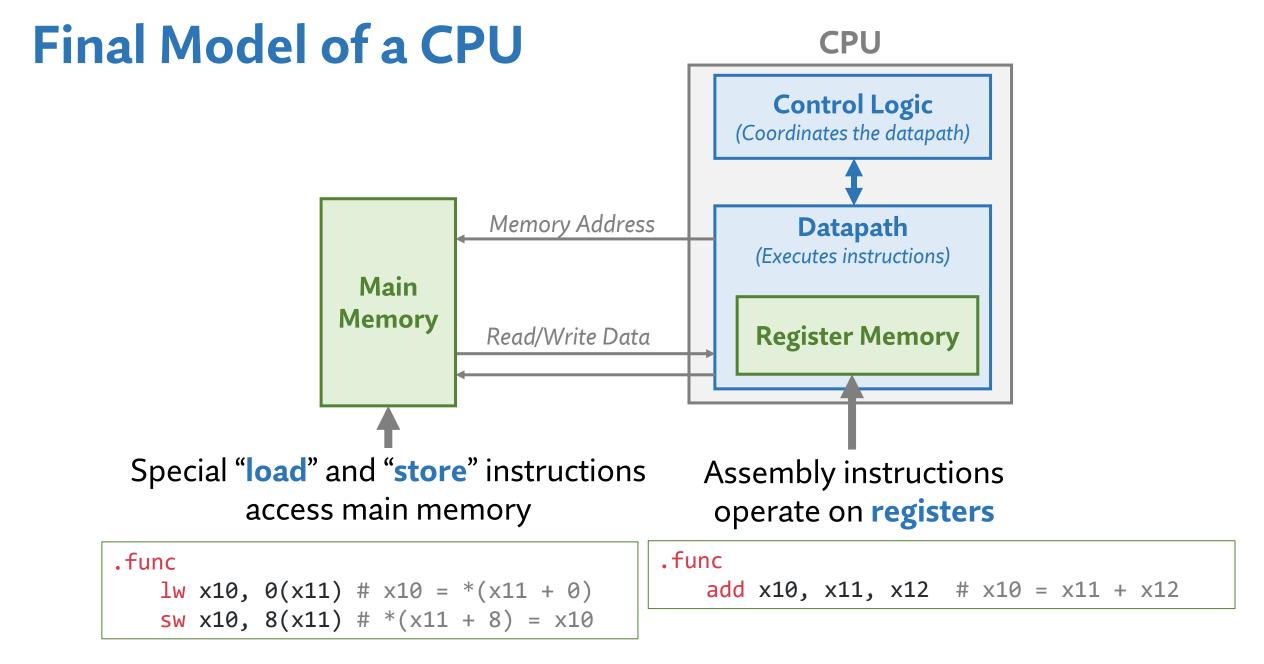

## **Inside a Processor Core: Overview**

#### **Two new memories!**

- Both are performance optimizations

- Beyond the C language abstraction

- Much faster to access than main memory

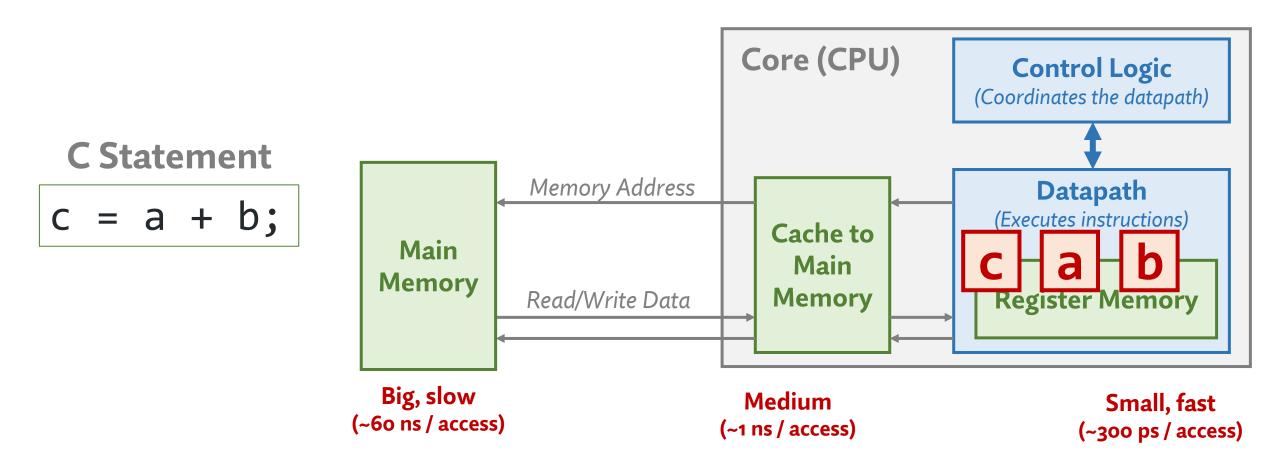

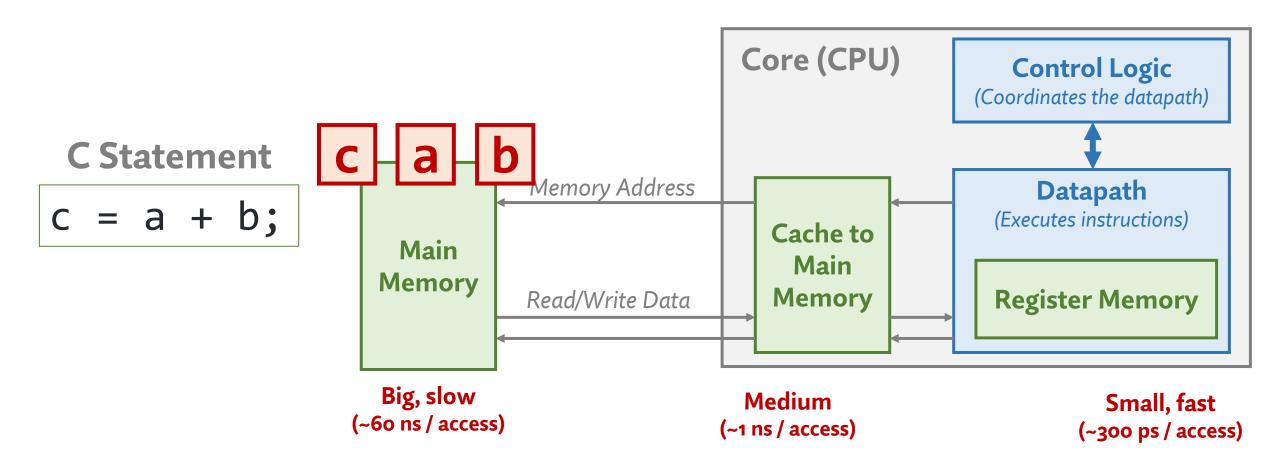

## **Performance: "c = a + b" In Register Memory**

## **Performance: "c = a + b" In Main Memory**

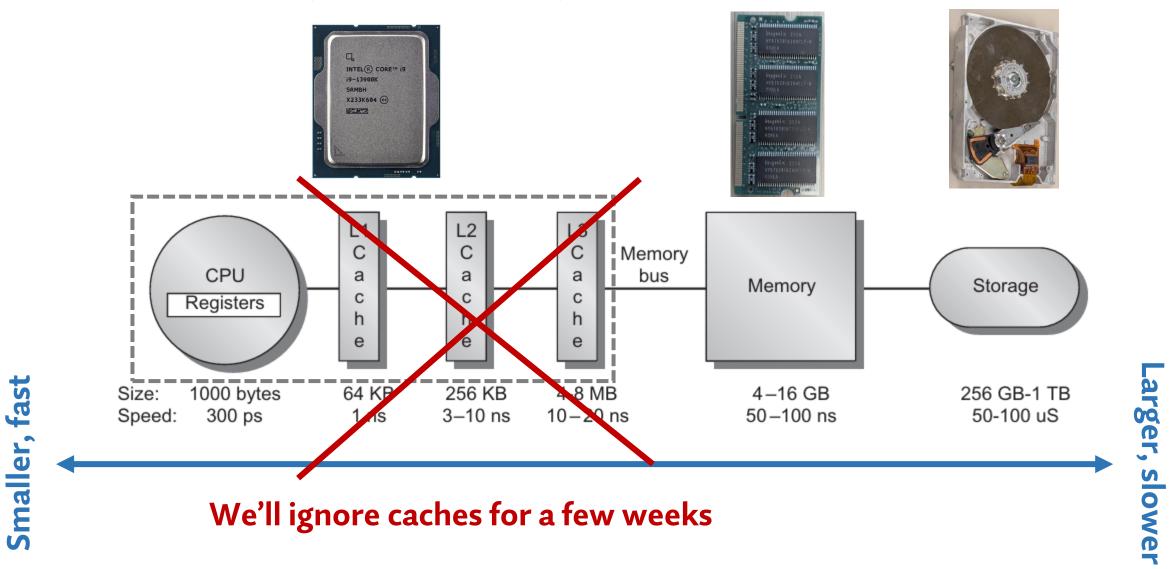

## **Aside: Memory Hierarchy**

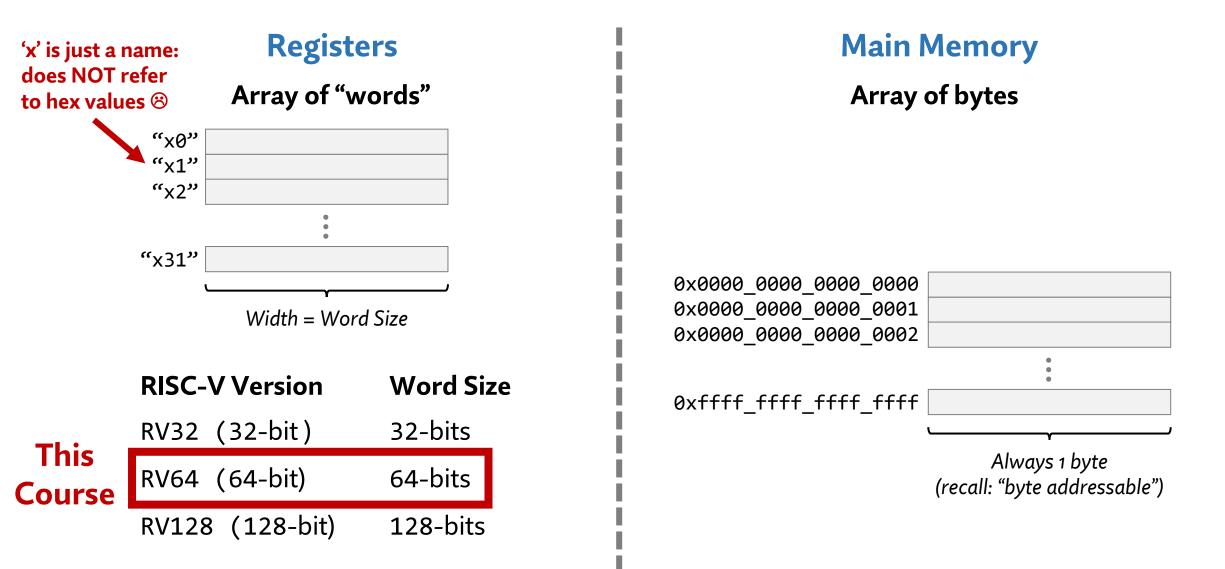

## **Registers vs. Main Memory**

# Agenda

## Inside a Processor

- Lots of Pictures

- Inside a Processor Core

- Cache and Register Memory

# •RISC-V Assembly

- Instructions and Opcodes

- Immediate Values

- •Function Arguments

## **Assembly Has No Type System**

- Every register is just a **collection of bits**

- Could represent....

- A memory address

- A register "address" (e.g., 6 = x6)

- A two's complement integer

- An unsigned integer

- A character

• ...

## • Your job to decide + keep track

#### **Register Memory**

| "x0" | 0x0000_0000_0000_0000 |

|------|-----------------------|

| "x1" | 0x0000_fe3a_0ff1_237a |

| "x2" | 0x0000_0000_0000_0006 |

|      |                       |

"x31" 0x0000\_0000\_0000\_0065

## **Special Registers**

#### • By convention, some registers are **reserved for specific uses**

| Register | ABI Name | Description                      | Ţ                |

|----------|----------|----------------------------------|------------------|

| x0       | zero     | Hard-wired zero                  | Ţ                |

| x1       | ra       | Return address                   |                  |

| x2       | sp       | Stack pointer                    |                  |

| x3       | gp       | Global pointer                   |                  |

| x4       | tp       | Thread pointer                   | We will mostly   |

| x5–7     | t0-2     | Temporaries                      |                  |

| x8       | s0/fp    | Saved register/frame pointer     | talk about these |

| x9       | s1       | Saved register                   |                  |

| x10-11   | a0-1     | Function arguments/return values |                  |

| x12–17   | a2–7     | Function arguments               |                  |

| x18–27   | s2–11    | Saved registers                  |                  |

| x28–31   | t3-6     | Temporaries                      |                  |

# Agenda

## Inside a Processor

- Lots of Pictures

- Inside a Processor Core

- Cache and Register Memory

## •RISC-V Assembly •Instructions and Opcodes

- Immediate Values

- •Function Arguments

## **Instruction Examples**

•Assembly programs have **one instruction** per line of source code

opcode rd,

r

(e.g., add, bit shift, load/store)rs1,

r

registerrs2

xadd x5, x6, x7Sub x5, x6, x7

$$x5 = x6 + x7$$

x5 = x6 + x7x5 = x6 - x7 $x5 = x6 - x7$

x18–27

x28–31

s2–11

t3-6

Temporaries

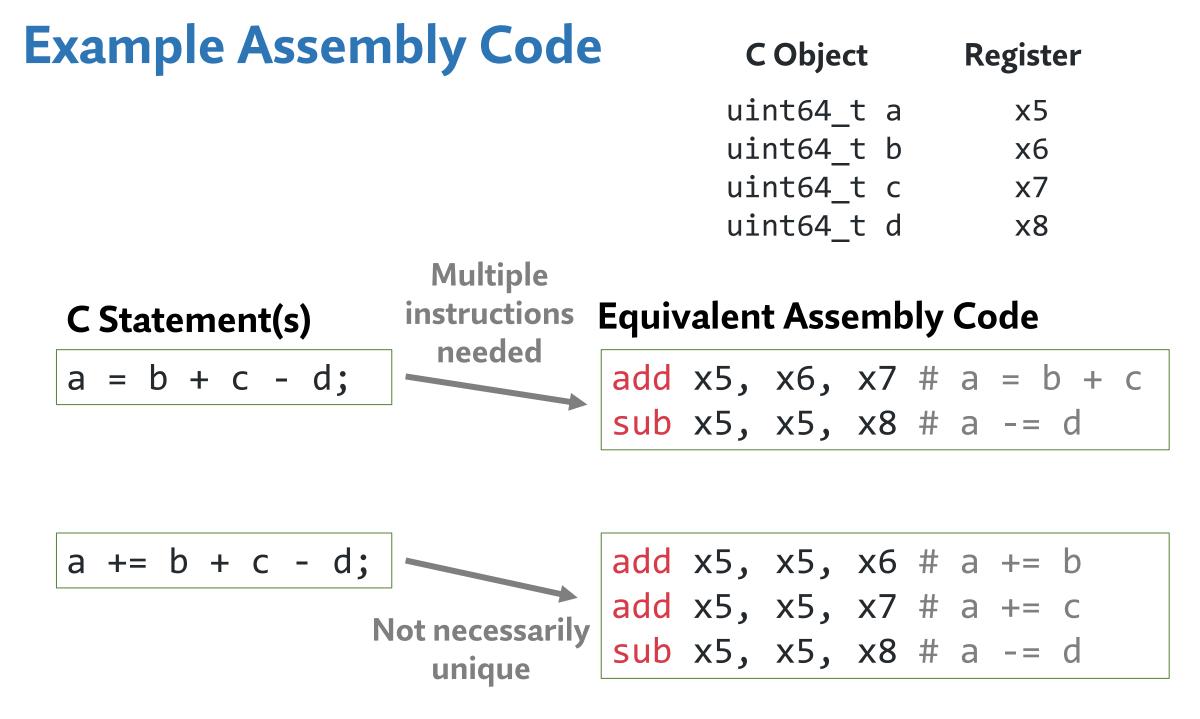

## **Comparing C and Assembly Code**

"Register Allocation"

| C Object   | Register |

|------------|----------|

| uint64_t a | x5       |

| uint64_t b | x6       |

| uint64_t c | x7       |

**C** Statement

## **Equivalent Assembly Code**

a = b + c;

add x5, x6, x7 #

$$a = b + c$$

**Python-style comments**

## **RV64i Reference Sheets**

BV64i Base Integer Instructions

## • We are using a **subset** of the RISC-V ISA called "**RV64i**"

~57 Total Instructions

| Opcode     | Instruction             | Fmt    | Example    | 2                      | Description                                      | Notes                        |

|------------|-------------------------|--------|------------|------------------------|--------------------------------------------------|------------------------------|

| 1i         | load immediate          | *      | 1i         | a0, 2                  | addi aO, zero, 2                                 | pseudo                       |

| la         | load address            | *      | la         | aO, symbol             | a0 = symbol                                      | pseudo, 2 instr              |

| add        | add                     | R      | add        | a0, a1, a2             | a0 = a1 + a2                                     |                              |

| sub        | subtract                | R      | sub        | a0, a1, a2             | a0 = a1 - a2                                     |                              |

| xor        | bitwise exclusive or    | R      | xor        | a0, a1, a2             | a0 = a1 ^ a2                                     |                              |

| or         | bitwise or              | R      | or         | a0, a1, a2             | a0 = a1   a2                                     |                              |

| and        | bitwise and             | R      | and        | a0, a1, a2             | a0 = a1 & a2                                     |                              |

| sll        | shift left logical      | R      | sll        | a0, a1, a2             | a0 = a1 << a2                                    |                              |

| srl        | shift right logical     | R      | srl        | a0, a1, a2             | a0 = a1 >> a2                                    |                              |

| sra        | shift right arith*      | R      | sra        | a0, a1, a2             | a0 = a1 >> a2                                    | sign-extends                 |

| slt        | set less than           | R      | slt        | a0, a1, a2             | a0 = (a1 < a2) ? 1 : 0                           |                              |

| sltu       | set less than (u)       | R      | sltu       | a0, a1, a2             | a0 = (a1 < a2) ? 1 : 0                           | unsigned                     |

| addi       | add immediate           | I      | addi       | a0, a1, 2              | a0 = a1 + 2                                      |                              |

| xori       | xor immediate           | I      | xori       | a0, a1, 2              | a0 = a1 ^ 2                                      |                              |

| ori        | or immediate            | I      | ori        | a0, a1, 2              | a0 = a1   2                                      |                              |

| andi       | and immediate           | I      | andi       | a0, a1, 2              | a0 = a1 & 2                                      |                              |

| slli       | shift left logical imm  | I      | slli       | a0, a1, 2              | a0 = a1 << 2                                     |                              |

| srli       | shift right logical imm | Î      | srli       | a0, a1, 2              | a0 = a1 >> 2                                     |                              |

| srai       | shift right arith imm   | i      | srai       | a0, a1, 2              | a0 = a1 >> 2                                     | sign-extends                 |

| slti       | set less than imm       | Î      | slti       | a0, a1, 2              | a0 = (a1 < 2) ? 1 : 0                            |                              |

| sltiu      | set less than imm (u)   | i      | sltiu      | a0, a1, 2              | a0 = (a1 < 2) ? 1 : 0                            | unsigned                     |

| mv         | move (copy)             | *      | mv         | a0, a1                 | addi a0, a1, 0                                   | pseudo                       |

| neg        | 2s-complement negation  | *      | neg        | a0, a1                 | sub a0, zero, a1                                 | pseudo                       |

| not        | bitwise not             | *      | not        | a0, a1                 | xori a0, a1, -1                                  | pseudo                       |

| 1b         | load byte               | I      | 1b         | a0, 1(a1)              | a0 = M[a1+1] (8 bits)                            | pscauo                       |

| 15<br>1h   | load half               | I      | 1b<br>1h   | a0, 2(a1)              | a0 = M[a1+1] (0 bits)<br>a0 = M[a1+2] (16 bits)  |                              |

| 14         | load word               | I      | 11         | a0, 2(a1)<br>a0, 4(a1) | a0 = M[a1+2] (10 bits)<br>a0 = M[a1+4] (32 bits) |                              |

| ld         | load double word        | I      | 10         | a0, 4(a1)<br>a0, 8(a1) | a0 = M[a1+4] (32 bits)<br>a0 = M[a1+8] (64 bits) |                              |

| la         | load byte (u)           | I      | 1a<br>1bu  | a0, 3(a1)<br>a0, 1(a1) | a0 = M[a1+0] (64 bits)<br>a0 = M[a1+1] (8 bits)  | zero-extends                 |

| lbu        |                         | I      |            |                        |                                                  |                              |

| lwu        | load half (u)           | I      | lhu<br>lwu | a0, 2(a1)<br>a0, 4(a1) | a0 = M[a1+2] (16 bits)<br>a0 = M[a1+4] (32 bits) | zero-extends<br>zero-extends |

|            | load word (u)           | *      | ld         |                        |                                                  |                              |

| 1{b h w d} | load global             |        |            | a0, symbol             | a0 = M[symbol]                                   | pseudo, 2 instr              |

| sb         | store byte              | S<br>S | sb         | a0, 1(a1)              | M[a1+1] = a0 (8 bits)                            |                              |

| sh         | store half              |        | sh         | a0, 2(a1)              | M[a1+2] = a0 (16 bits)                           |                              |

| sw         | store word              | S      | sw         | a0, 4(a1)              | M[a1+4] = a0 (32 bits)                           |                              |

| sd         | store double word       | S<br>* | sd         | a0, 8(a1)              | M[a1+8] = a0 (64 bits)                           |                              |

| s{b h w d} | store global            |        | sd         | aO, symbol, tO         | M[symbol] = a0 (uses t0)                         | pseudo, 2 instr              |

| beq        | branch if =             | В      | beq        | a0, a1, 2b             | if (a0 == a1) goto 2b                            |                              |

| bne        | branch if ≠             | В      | bne        | a0, a1, 2f             | if (a0 != a1) goto 2f                            |                              |

| blt        | branch if <             | В      | blt        | a0, a1, 2b             | if (a0 < a1) goto 2b                             |                              |

| ble        | branch if $\leq$        | *      | ble        | a0, a1, 2f             | bge a1, a0, 2f                                   | pseudo                       |

| bgt        | branch if >             | *      | bgt        | a0, a1, 2b             | blt a1, a0, 2b                                   | pseudo                       |

| bge        | branch if $\geq$        | В      | bge        | a0, a1, 2f             | if (a0 >= a1) goto 2f                            |                              |

| bltu       | branch if $<$ (u)       | В      | bltu       | a0, a1, 2b             | if (a0 < a1) goto 2b                             | unsigned                     |

| bleu       | branch if $\leq$ (u)    | *      | bleu       | a0, a1, 2f             | bgeu a1, a0, 2f                                  | unsigned, pseu               |

| bgtu       | branch if > (u)         | *      | bgtu       | a0, a1, 2b             | bltu a1, a0, 2b                                  | unsigned, pseu               |

| bgeu       | branch if $\geq$ (u)    | В      | bgeu       | a0, a1, 2f             | if (a0 >= a1) goto 2f                            | unsigned                     |

| beqz       | branch if $= 0$         | *      | beqz       | a0, 2b                 | if (a0 == 0) goto 2b                             | pseudo                       |

| bnez       | branch if $\neq 0$      | *      | bnez       | a0, 2f                 | if (a0 != 0) goto 2f                             | pseudo                       |

| bltz       | branch if $< 0$         | *      | bltz       | a0, 2b                 | if (a0 < 0) goto 2b                              | pseudo                       |

| blez       | branch if $\leq 0$      | *      | blez       | a0, 2f                 | if (a0 <= 0) goto 2f                             | pseudo                       |

| bgtz       | branch if $\ge 0$       | *      | bgtz       | a0, 2b                 | if (a0 > 0) goto 2b                              | pseudo                       |

| bgez       | branch if $\geq 0$      | *      | bgez       | a0, 2f                 | if (a0 >= 0) goto 2f                             | pseudo                       |

| jal        | jump and link           | J      | jal        | ra, label              | ra = pc+4; jump to label                         |                              |

| jalr       | jump and link reg       | I      | jalr       | ra, al                 | ra = pc+4; jump to a1                            |                              |

| call       | call subroutine         | *      | call       | label                  | ra = pc+4; jump to label                         |                              |

| j          | jump                    | *      | j          | label                  | jump to label                                    |                              |

| lui        | load upper imm          | U      | lui        | a0, 1234               | a0 = 1234 << 12                                  |                              |

| auipc      | add upper imm to pc     | Ŭ      | auipc      | a0, 1234               | a0 = pc + (1234 << 12)                           |                              |

| ecall      | environment call        | I      | ecall      | , 1601                 | system call (calls the OS)                       |                              |

| ebreak     | environment break       | I      | ebreak     |                        | break to debugger                                |                              |

| entear     | envnonment break        | 1      | ebreak     |                        | preav to depublic                                | 1                            |

https://www.cs.utahtech.edu/cs/2810/riscv-card.pdf

| Base Integer           | Inct            | ructio      | ns RV32T R            | 1641 and                |                         |          |                   | <b>RV</b> Privileged     |             |                          |

|------------------------|-----------------|-------------|-----------------------|-------------------------|-------------------------|----------|-------------------|--------------------------|-------------|--------------------------|

| Category Name          | Fmt             |             | RV32I Base            |                         | {64,128}                |          | Categor           |                          |             | V mnemonic               |

| Loads Load Byte        | I               | LB .        | rd,rs1,imm            |                         | [01/120]                |          | CSR Acc           |                          |             | rd,csr,rs1               |

| Load Halfword          | ī               | LH          | rd,rs1,imm            |                         |                         |          |                   | omic Read & Set Bi       |             | rd,csr,rs1               |

| Load Word              | I               | LW          | rd,rs1,imm            | L{DQ}                   | rd,rs1,                 | imm      |                   | nic Read & Clear Bi      |             | rd,csr,rs1               |

| Load Byte Unsigned     | ī               | LBU         | rd,rs1,imm            | -(-/2)                  |                         |          |                   | Atomic R/W Imr           |             |                          |

| Load Half Unsigned     | Î               | LHU         | rd,rs1,imm            | L{W D}U                 | rd,rs1,                 | imm      | Atomic            | Read & Set Bit Imr       |             |                          |

| Stores Store Byte      | S               | SB          | rs1,rs2,imm           | 2(                      | 24/202/                 |          |                   | ead & Clear Bit Imr      |             |                          |

| Store Halfword         | S               | SH          | rs1,rs2,imm           |                         |                         |          | Change            |                          |             | 14/001/1144              |

| Store Word             | s               | SW          | rs1,rs2,imm           | S{DQ}                   | rs1,rs2                 | imm      |                   | onment Breakpoint        |             |                          |

| Shifts Shift Left      | R               | SLL         |                       | SLL{WD}                 |                         |          |                   |                          |             |                          |

| Shift Left Immediate   |                 |             | rd,rs1,rs2            |                         |                         |          |                   | Environment Retur        |             |                          |

|                        | I<br>R          | SLLI<br>SRL | rd,rs1,shamt          | SLLI {W   D}            |                         |          |                   | lirect to Supervis       |             |                          |

| Shift Right            |                 |             | rd,rs1,rs2            | SRL{W D}                |                         |          |                   | t Trap to Hyperviso      |             |                          |

| Shift Right Immediate  | I               | SRLI        | rd,rs1,shamt          | SRLI {W   D}            |                         |          |                   | r Trap to Superviso      |             |                          |

| Shift Right Arithmetic | R               | SRA         | rd,rs1,rs2            | SRA{W D}                |                         |          |                   | t Wait for Interru       |             |                          |

| Shift Right Arith Imm  | I               | SRAI        | rd,rs1,shamt          | SRAI {W D}              |                         |          | мми               | Supervisor FENC          | SFENCE      | .VM rs1                  |

| Arithmetic ADD         | R               | ADD         | rd,rs1,rs2            | ADD {W   D}             |                         |          |                   |                          |             |                          |

| ADD Immediate          | I               | ADDI        | rd,rs1,imm            | ADDI{WD}                |                         |          |                   |                          |             |                          |

| SUBtract               | R               | SUB         | rd,rs1,rs2            | SUB{W D}                |                         |          |                   |                          |             |                          |

| Load Upper Imm         | U               | LUI         | rd,imm                |                         |                         |          | sed (16-          | bit) Instructio          |             |                          |

| Add Upper Imm to PC    | U               | AUIPC       | rd,imm                | Category                | Name                    | Fmt      |                   | RVC                      |             | VI equivalent            |

| Logical XOR            | R               | XOR         | rd,rs1,rs2            |                         | oad Word                | CL       |                   | rd',rs1',imm             |             | ,rs1′,imm*4              |

| XOR Immediate          | I               | XORI        | rd,rs1,imm            | Loa                     | d Word SP               | CI       | C.LWSP            | rd,imm                   | LW rd,      | sp,imm*4                 |

| OR                     | R               | OR          | rd,rs1,rs2            | Lo                      | ad Double               | CL       | C.LD              | rd',rs1',imm             | LD rd'      | ,rs1',imm*8              |

| OR Immediate           | I               | ORI         | rd,rs1,imm            | Load                    | Double SP               | CI       | C.LDSP            | rd,imm                   | LD rd,      | sp,imm*8                 |

| AND                    | R               | AND         | rd,rs1,rs2            | ι I                     | oad Quad                | CL       | C.LQ              | rd',rs1',imm             |             | ,rs1',imm*1              |

| AND Immediate          | I               | ANDI        | rd,rs1,imm            | Load                    | d Quad SP               | CI       | C.LOSP            | rd,imm                   | LO rd.      | sp,imm*16                |

| Compare Set <          | R               | SLT         | rd,rs1,rs2            | Stores St               |                         | CS       |                   | rs1',rs2',imm            |             | ',rs2',imm*              |

| Set < Immediate        | I               | SLTI        | rd,rs1,imm            |                         | e Word SP               | CSS      | C.SWSP            | rs2,imm                  |             | ,sp,imm*4                |

| Set < Unsigned         | R               | SLTU        | rd,rs1,rs2            | Sto                     | re Double               | CS       |                   | rs1',rs2',imm            |             | ',rs2',imm*              |

| Set < Imm Unsigned     | I               |             | rd,rs1,imm            |                         | Double SP               | CSS      |                   | rs2,imm                  |             | ,sp,imm*8                |

| Branches Branch =      | SB              | BEO         | rs1,rs2,imm           |                         | tore Quad               | CS       |                   | rs1',rs2',imm            |             | ',rs2',imm*              |

| Branch ≠               | SB              | BNE         | rs1,rs2,imm           |                         | e Ouad SP               | CSS      | -                 | rs2,imm                  |             | sp,imm*16                |

| Branch <               | SB              | BLT         | rs1,rs2,imm           | Arithmeti               |                         | CR       | C.ADD             | rd,rs1                   | ADD         | rd,rd,rs1                |

| Branch ≥               | SB              | BGE         | rs1,rs2,imm           |                         | ADD Word                | CR       | C.ADD<br>C.ADDW   | rd,rs1                   |             | rd,rd,imm                |

| Branch < Unsigned      | SB              | BLTU        | rs1,rs2,imm           |                         | mmediate                | CI       | C.ADDW            | rd,imm                   |             | rd,rd,imm                |

| Branch $\geq$ Unsigned | SB              | BGEU        | rs1,rs2,imm           |                         | Nord Imm                | CI       | C.ADDI<br>C.ADDIW |                          |             |                          |

| Jump & Link J&L        | <u>56</u><br>U1 | JAL         | rs1,rs2,1mm<br>rd.imm |                         | Imm * 16                | CI       |                   | rd,imm<br>SP x0,imm      | ADDIW       | rd,rd,imm<br>sp,sp,imm*1 |

| Jump & Link Register   | UJ              | JAL         | rd,1mm<br>rd,rs1,imm  |                         | 2 Imm * 16<br>2 Imm * 4 | CIW      |                   | SP x0,1mm<br>SPN rd',1mm |             | rd', sp, imm*1           |

| Synch Synch thread     | I               | FENCE       | ra, rsi, inud         |                         | mmediate                | CIW      | C.LI              | rd,imm                   | ADDI        | rd,x0,imm                |

| Synch Instr & Data     | I               | FENCE       | т.                    |                         | pper Imm                | CI       | C.LUI             |                          | LUI         |                          |

| System System CALL     | _               | SCALL       | • 1                   | Load U                  | pper 1mm<br>MoVe        | CR       | C.LUI             | rd,imm                   | ADD         | rd,imm                   |

| System BREAK           | I<br>I          | SCALL       | ,                     |                         | SUB                     | CR       |                   | rd,rs1                   | SUB         | rd,rs1,x0                |

| Counters ReaD CYCLE    |                 |             |                       | Shifts Shift            |                         | CI       | C.SUB             | rd,rs1                   |             | rd,rd,rs1                |

|                        | I               | RDCYC       |                       | Branches                |                         |          | C.SLLI            | rd,imm                   | SLLI        | rd,rd,imm                |

| ReaD CYCLE upper Half  | I<br>I          | RDCYC       |                       |                         |                         | CB       | C.BEQZ            | rs1',imm                 | BEQ         | rs1',x0,imm              |

| ReaD TIME              | -               | RDTIM       |                       |                         | Branch≠0                | CB       | C.BNEZ            | rs1',imm                 | BNE         | rs1',x0,imm              |

| ReaD TIME upper Half   | I               | RDTIM       |                       | Jump                    | Jump                    | CJ       | C.J               | imm                      | JAL         | x0,imm                   |

| ReaD INSTR RETired     | I               | RDINS       |                       |                         | p Register              | CR       | C.JR              | rd,rs1                   |             | x0,rs1,0                 |

| ReaD INSTR upper Half  | I               | RDINS       | TRETH rd              | Jump & Li<br>Jump & Lin |                         | CJ<br>CR | C.JAL             | imm                      | JAL<br>JALR | ra,imm                   |

|                        |                 |             |                       |                         |                         |          | C.JALR            | rs1                      |             | ra,rs1,0                 |

#### https://www.cl.cam.ac.uk/teaching/1617/ECAD+Arc h/files/docs/RISCVGreenCardv8-20151013.pdf

## **RISC-V Instruction Set Manual**

#### The RISC-V Instruction Set Manual Volume I

Unprivileged Architecture

Version 20240411

#### Example: ADD/SUB/AND/OR/XOR/SHIFT

#### 2.4.2. Integer Register-Register Operations

RV32I defines several arithmetic R-type operations. All operations read the *rs1* and *rs2* registers as source operands and write the result into register *rd*. The *funct7* and *funct3* fields select the type of operation.

| 31 25                                                                                                                                                                                                                                                                                                                                                                               | 24 20 19         | 15 14 12                                                              | 11 7 6                                    | 0                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------|-------------------------------------------|---------------------------------|

| funct7                                                                                                                                                                                                                                                                                                                                                                              | rs2              | rs1 funct3                                                            | rd                                        | opcode                          |

| 7           0         0         0         0         0         0           0         0         0         0         0         0         0           0         0         0         0         0         0         0         0           0         0         0         0         0         0         0         0           0         1         0         0         0         0         0 | src2 s<br>src2 s | 5 3<br>rc1 ADD/SLT[U]<br>rc1 AND/OR/XOR<br>rc1 SLL/SRL<br>rc1 SUB/SRA | 5<br>dest<br>dest<br>dest<br>dest<br>dest | 7<br>OP<br>OP<br>OP<br>OP<br>OP |

ADD performs the addition of *rs1* and *rs2*. SUB performs the subtraction of *rs2* from *rs1*. Overflows are ignored and the low XLEN bits of results are written to the destination *rd*. SLT and SLTU perform signed and unsigned compares respectively, writing 1 to *rd* if *rs1 < rs2*, 0 otherwise. Note, SLTU *rd*, *x*0, *rs2* sets *rd* to 1 if *rs2* is not equal to zero, otherwise sets *rd* to zero (assembler pseudoinstruction SNEZ *rd*, *rs*). AND, OR, and XOR perform bitwise logical operations.

SLL, SRL, and SRA perform logical left, logical right, and arithmetic right shifts on the value in register *rs1* by the shift amount held in the lower 5 bits of register *rs2*.

## **Bitwise Instructions**

"Register Allocation"

| C Object   | Register |

|------------|----------|

| uint64_t a | x5       |

| uint64_t b | x6       |

| uint64 t c | x7       |

#### **C** Statement

### **Equivalent Assembly Code**

## Logical (Unsigned) Bit Shifts

"Register Allocation"

| C Object   | Register |

|------------|----------|

| uint64_t a | x5       |

| uint64_t b | x6       |

| uint64 t c | x7       |

#### **C** Statement

## Arithmetic (Signed) Bit Shifts

"Register Allocation"

| C Object  | Register |

|-----------|----------|

| int64_t a | x5       |

| int64_t b | x6       |

| int64 t c | x7       |

#### **C** Statement

### **Equivalent Assembly Code**

<does not exist>

## **Register Copy**

"Register Allocation"

| C Object   | Register |

|------------|----------|

| uint64_t a | x5       |

| uint64_t b | хб       |

#### **C** Statement

## Equivalent Assembly Code

## **Pseudo-Instruction**

Syntactic sugar to the assembler (not a machine code instruction)

| Register | ABI Name | Description                      |

|----------|----------|----------------------------------|

| x0       | zero     | Hard-wired zero                  |

| x1       | ra       | Return address                   |

| x2       | sp       | Stack pointer                    |

| x3       | gp       | Global pointer                   |

| x4       | tp       | Thread pointer                   |

| x5–7     | t0-2     | Temporaries                      |

| x8       | s0/fp    | Saved register/frame pointer     |

| x9       | s1       | Saved register                   |

| x10-11   | a0-1     | Function arguments/return values |

| x12–17   | a2–7     | Function arguments               |

| x18–27   | s2–11    | Saved registers                  |

| x28–31   | t3-6     | Temporaries                      |

# Agenda

## Inside a Processor

- Lots of Pictures

- Inside a Processor Core

- Cache and Register Memory

- •RISC-V Assembly •Instructions and Opcodes

- Immediate Values

- •Function Arguments

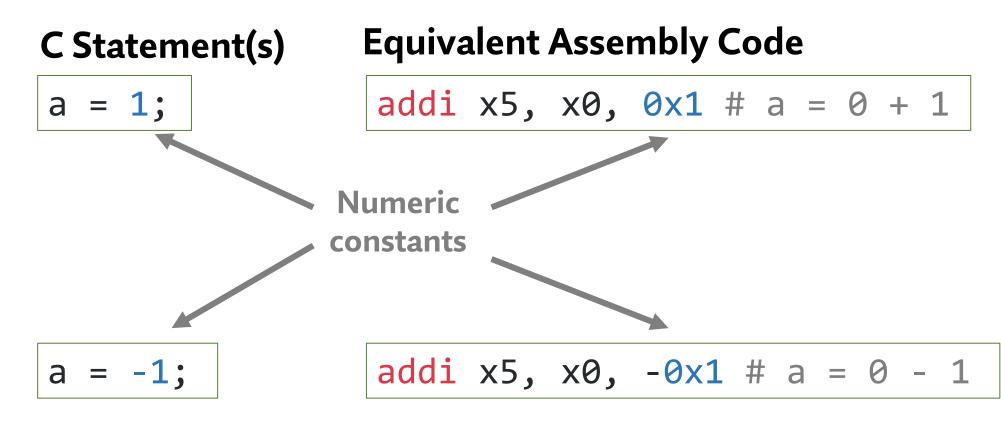

## **Immediate Values**

**C Object** Register uint64\_t a x5

| Register | ABI Name | Description                      |

|----------|----------|----------------------------------|

| x0       | zero     | Hard-wired zero                  |

| x1       | ra       | Return address                   |

| x2       | sp       | Stack pointer                    |

| x3       | gp       | Global pointer                   |

| x4       | tp       | Thread pointer                   |

| x5–7     | t0-2     | Temporaries                      |

| x8       | s0/fp    | Saved register/frame pointer     |

| x9       | s1       | Saved register                   |

| x10-11   | a0-1     | Function arguments/return values |

| x12–17   | a2–7     | Function arguments               |

| x18–27   | s2–11    | Saved registers                  |

| x28–31   | t3-6     | Temporaries                      |

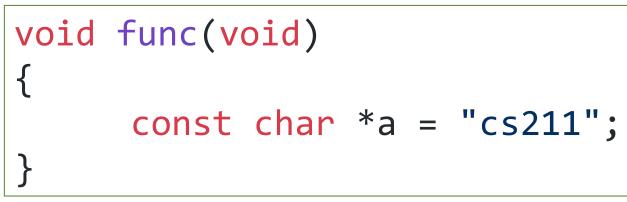

## **String Constants**

C Object Register

char \*a

x5

## C Statement(s)

## RV64i So Far

## Instructions

**Register-Register Arithmetic**

| add  | rd,   | rs1,   | rs2 |

|------|-------|--------|-----|

| sub  | rd,   | rs1,   | rs2 |

| and  | rd,   | rs1,   | rs2 |

| or r | rd, r | rs1, r | rs2 |

| xor  | rd,   | rs1,   | rs2 |

| sll  | rd,   | rs1,   | rs2 |

| srl  | rd,   | rs1,   | rs2 |

| sra  | rd,   | rs1,   | rs2 |

**Register-Immediate Arithmetic**

addi rd, rs1, imm

### **Pseudo-Instructions**

.asciz <C-style string>

mv rd, rs1

# Agenda

## Inside a Processor

- Lots of Pictures

- Inside a Processor Core

- Cache and Register Memory

## •RISC-V Assembly •Instructions and Opcodes

- Immediate Values

- Function Arguments

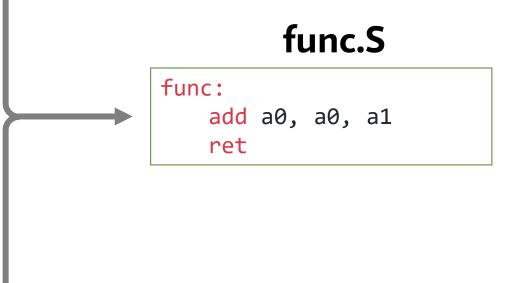

## **C** Function Calling Conventions

- Function arguments are in a0-a7

- Return values are in a0 (+a1, if >64 bits)

- Narrower C types are sign/zero extended

#### func.c

| int                        | // return: a0 |

|----------------------------|---------------|

| <pre>func(uint8_t a,</pre> | // a: a0      |

| uint16_t b,                | // b: a1      |

| char *c,                   | // c: a2      |

| uint64_t d,                | // d: a3      |

| int e,                     | // e: a4      |

| char f,                    | // f: a5      |

| unsigned int g,            | // g: a6      |

| <b>void</b> *****h)        | // h: a7      |

| {                          |               |

| <pre>return a + b;</pre>   |               |

| }                          |               |

| ABI Name | Description                      |  |

|----------|----------------------------------|--|

| zero     | Hard-wired zero                  |  |

| ra       | Return address                   |  |

| sp       | Stack pointer                    |  |

| gp       | Global pointer                   |  |

| tp       | Thread pointer                   |  |

| t0-2     | Temporaries                      |  |

| s0/fp    | Saved register/frame pointer     |  |

| s1       | Saved register                   |  |

| a0-1     | Function arguments/return values |  |

| a2–7     | Function arguments               |  |

| s2–11    | Saved registers                  |  |

| t3-6     | Temporaries                      |  |

## CS 211: Intro to Computer Architecture 9.2: RISC-V Assembly

## **Minesh Patel** Spring 2025 – Thursday 27 March